### DESCRIPTION

The Accutek AK632256W-72 SRAM Module consists of fast high performance SRAMs mounted on a low profile, 72 pin SIM Board. The module utilizes four 28 pin 256K x 4 SRAMs in 400 mil SOJ packages and four decoupling capacitors mounted on each side of a printed circuit board.

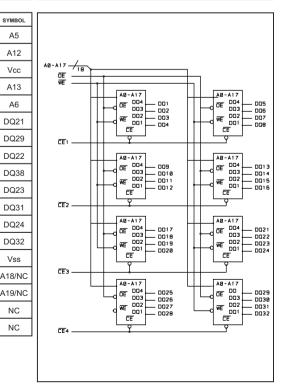

The SRAMs used have common I/O functions and single output enable functions. Also, four separate chip select (CE) connections are used to independently enable the four bytes. The modules can be supplied in a variety of access time values from 12 nSEC to 45 nSEC in CMOS or BiCMOS technology.

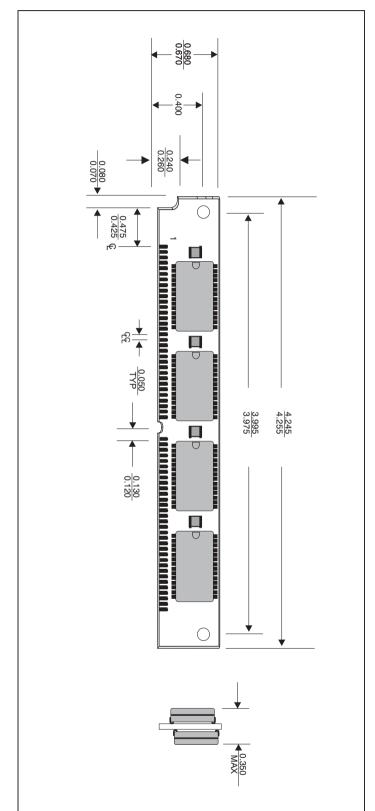

The Accutek module is designed to have a maximum seated height of 0.680 inch to provide for the lowest height off the board. By offset-mounting the back surface SRAMs the module can be mounted in either angled or straight-up SIM sockets. The module conforms to JEDEC standard sizes and pin-out configurations. Using four pins for module memory density identification, PD<sub>0</sub> to PD<sub>3</sub>, minimizes interchangeability and design considerations when changing from one module size to another in customer applications.

## **FEATURES**

- 262,144 x 32 bit organization

- JEDEC Standardized 72 pin SIM or ZIP pinout

- Common I/O, single OE functions with four separate chip selects (CE)

- Low height, 0.680 inch maximum

- Upward compatible with 512K x 32 (AK632512) and 1 Meg x 32 (AK6321024)

# **PIN NOMENCLATURE**

| A <sub>0</sub> - A <sub>17</sub>    | Address Inputs   |    | PIN # | SYMBOL |

|-------------------------------------|------------------|----|-------|--------|

|                                     |                  |    | 1     | NC     |

| $\overline{CE}_1 - \overline{CE}_4$ | Chip Enable      |    | 2     | NC     |

| DQ1 - DQ32                          | Data In/Data Out |    | 3     | PD2/NC |

| OE                                  | Output Enable    |    | 4     | PD3/NC |

| -                                   |                  |    | 5     | Vss    |

| PD <sub>0</sub> - PD <sub>3</sub>   | Presence Detect  |    | 6     | PD0    |

| Vcc                                 | 5v Supply        |    | 7     | PD1    |

| Vss                                 | Ground           |    | 8     | DQ1    |

|                                     |                  |    | 9     | DQ9    |

| WE                                  | Write Enable     |    | 10    | DQ2    |

| NC                                  | No Connect       |    | 11    | DQ10   |

|                                     |                  |    | 12    | DQ3    |

|                                     |                  |    | 13    | DQ11   |

| MODULE OPTIONS                      |                  |    | 14    | DQ4    |

|                                     |                  |    | 15    | DQ12   |

| Leadless SIM: AK632256W-72          |                  | 16 | Vcc   |        |

|                                     |                  |    | 17    | A0     |

# AK632256W-72 262.144 x 32 Bit CMOS/BiCMOS 72 Pin Format Static Random Access Memory

- Downward compatible with 32K x 32 (AK63232), 64K x 32 (AK63264) and 128K x 32 AK632128

- Presence Detect PD<sub>0</sub> to PD<sub>3</sub> for identifying module density

- Fast access times range from 12 nSEC BiCMOS to 45 nSEC CMOS

- · TTL-compatible inputs and outputs

- Single 5 volt power supply AK632256W-72

- Single 3.3 volt power supply AK632256W-72/3.3

- Operating temperature range in free air, 0<sup>0</sup>C to 70<sup>0</sup>C

### **ELECTRICAL SPECIFICATIONS**

Timing diagrams and basic electrical characteristics are those of the standard 256K x 4 SRAMs used to construct these modules. Accutek's module design allows the flexibility of selecting industrv-compatible 256K x 4 SRAMs from several semiconductor manufacturers

## FUNCTIONAL DIAGRAM

# PIN ASSIGNMENT

PIN #

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

18

A7

PD0 = Vss

PD1 = Vss

SYMBOL

A1

A8

A2

A9

DQ13

DQ5

DQ14

DQ15

DQ7

DQ16

DQ8

Vss

WE

A15

A14

CE2

CE1

PIN #

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

SYMBOL

CE4

CE3

A17

A16

OE

Vss

DQ25

DQ17

DQ26

DQ18

DQ27

DQ19

DQ28

DQ20

A3

A10

A4

A11

PIN #

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

SYMBOL

A5

A12

Vcc

A13

A6

DQ21

DQ29

DQ22

DQ38

DQ23

DQ24

Vss

NC

NC

PD2 = Open PD3 = Open

# **ORDERING INFORMATION**

| P   | ART NUMBER CODING INTERPRETATION                                                                                                                                                                                                                                                              |   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Pos | sition 1 2 3 4 5 6 7 8                                                                                                                                                                                                                                                                        | 3 |

| 1   | Product                                                                                                                                                                                                                                                                                       |   |

|     | AK = Accutek Memory                                                                                                                                                                                                                                                                           |   |

| 2   | Type<br>4 = Dynamic RAM<br>5 = CMOS Dynamic RAM<br>6 = Static RAM                                                                                                                                                                                                                             |   |

| 3   | Organization/Word Width                                                                                                                                                                                                                                                                       |   |

|     | 1 = by 1 16 = by 16<br>4 = by 4 32 = by 32<br>8 = by 8 36 = by 36<br>9 = by 9                                                                                                                                                                                                                 |   |

| 4   | Size/Bits Depth                                                                                                                                                                                                                                                                               |   |

|     | 64 = 64K 4096 = 4 MEG<br>256 = 256K 8192 = 8 MEG<br>1024 = 1 MEG 16384 = 16 MEG                                                                                                                                                                                                               |   |

| 5   | Package Type                                                                                                                                                                                                                                                                                  |   |

| 6   | G = Single In-Line Package (SIP)<br>S = Single In-Line Module (SIM)<br>D = Dual In-Line Package (DIP)<br>W = .050 inch Pitch Edge Connect<br>Z = Zig-Zag In-Line Package (ZIP)<br>Special Designation<br>P = Page Mode<br>N = Nibble Mode<br>K = Static Column Mode<br>W = Write Per Bit Mode |   |

| 7   | V = Video Ram                                                                                                                                                                                                                                                                                 |   |

| 7   | <ul> <li>Separator</li> <li>Commercial 0<sup>0</sup>C to +70<sup>0</sup>C</li> <li>M = Military Equivalent Screened<br/>(-55<sup>0</sup>C to +125<sup>0</sup>C)</li> <li>I = Industrial Temperature Tested<br/>(-45<sup>0</sup>C to +85<sup>0</sup>C)</li> <li>X = Burned In</li> </ul>       |   |

| 8   | Speed (first two significant digits)<br>DRAMS SRAMS                                                                                                                                                                                                                                           |   |

|     | $50 = 50 \text{ nS} \qquad 8 = 8 \text{ nS} \\60 = 60 \text{ nS} \qquad 10 = 10 \text{ nS} \\70 = 70 \text{ nS} \qquad 12 = 12 \text{ nS} \\80 = 80 \text{ nS} \qquad 15 = 15 \text{ nS}$                                                                                                     |   |

The numbers and coding on this page do not include all variations available but are shown as examples of the most widely used variations. Contact Accutek if other information is required.

## EXAMPLES:

#### AK632256W72-12

256K x 32, 12 nSEC SRAM Module, 72 Pin SIM Configuration

ACCUTEK MICROCIRCUIT CORPORATION BUSINESS CENTER at NEWBURYPORT 2 NEW PASTURE ROAD, SUITE 1 NEWBURYPORT, MA 01950-4054 PHONE: 978-465-6200 FAX: 978-462-3396 Email: sales@accutekmicro.com Internet: www.accutekmicro.com

## **MECHANICAL DIMENSIONS**

#### Inches

Accutek reserves the right to make changes in specifications at any time and without notice. Accutek does not assume any responsibility for the use of any circuitry described; no circuit patent licenses are implied. Preliminary data sheets contain minimum and maximum limits based upon design objectives, which are subject to change upon full characterization over the specific operating conditions.